Что является ячейкой статической памяти

Характеризация статических ячеек памяти

Рубрика: Технические науки

Дата публикации: 21.08.2016 2016-08-21

Статья просмотрена: 676 раз

Библиографическое описание:

Магеррамов, Р. В. Характеризация статических ячеек памяти / Р. В. Магеррамов. — Текст : непосредственный // Молодой ученый. — 2016. — № 17 (121). — С. 57-60. — URL: https://moluch.ru/archive/121/33373/ (дата обращения: 17.12.2021).

Память — устройство хранение данных (информации), запоминающее устройство. Физическое устройство, используемое в вычислениях и хранении определённых данных в течение заданного времени. Память является неизменной и незаменимой частью компьютерных устройств, начиная с 1940-х годов.

Ячейка памяти — это минимально-возможный адресуемый элемент памяти (запоминающего устройства). Данная ячейка может иметь различную емкость, длину и число разрядов. Также ячейки памяти присваивается адрес (порядковый номер) с помощью которого происходит обращение команды процессора к памяти.

Можно выделить два основных вида ячеек памяти построенных на полупроводниковых технологиях: (SRAM) — статическая память, не требующая регулярного обновления, (DRAM) — динамическая память, которая нуждается в периодической перезаписи для сохранения информации. Из этого следует, что в основном из статических ячеек памяти организуют кеши, а при помощи динамической памяти — ОЗУ.

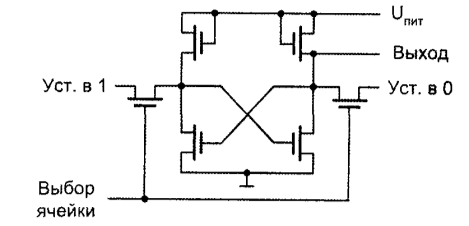

SRAM (static random access memory) — статическая память с произвольным доступом (Рисунок 1). Это полупроводниковая оперативная память, в которой каждый разряд (двоичный или троичный) хранится с положительной обратной связью в схеме, которая в отличии от динамической памяти (DRAM) позволяет поддерживать определенное состояние без регенерации. Однако сохранение данных без перезаписи в SRAM возможно только пока есть питание, из этого следует, что SRAM является энергозависимым типом памяти. С помощью произвольного доступа (RAM — random access memory) возможно осуществлять выбор для записи или чтения любой из битов, в отличие от конструкции памяти с последовательным доступом (SAM — sequential access memory).

Рис. 1. Электрическая схема запоминающего элемента SRAM

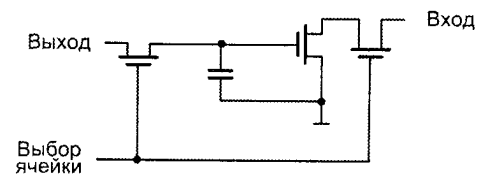

DRAM (dynamic random access memory) — динамическая память с произвольным доступом (Рисунок 2). Это энергозависимая полупроводниковая память, которая имеет произвольный доступ. Данный тип памяти широко используется в качестве оперативной памяти в нынешних компьютерных устройствах, а также для постоянного хранилища данных (информации).

Рис. 2. Электрическая схема запоминающего элемента DRAM

Устройства памяти являются одним из основных компонентов современной электроники. Нынешняя тенденция современных КМОП технологий — это стремление к постоянному уменьшению размеров элементов, снижение энергопотребления интегральных схем. Из этого следует много положительных моментов, однако в связи с уменьшением размеров интегральных компонентов возникает ряд проблем, связанных с технологическим разбросом транзисторных характеристик и линий связи. Данная проблематика в особенности ярко выражается при проектировании устройств памяти.

На Рисунке 1 представлена классическая 6-ти транзисторная ячейка статической памяти. Так как используются одни и те же шины для входной и выходной информации, операцию записи и чтения невозможно выполнить в один момент времени.

Устойчивость работы статических ячеек памяти напрямую зависит от изменения параметров транзисторов и линий их связи, в зависимости от технологии их изготовления. Из-за разбросов технологических параметров следует изменение важных характеристик транзисторов, таких как порог, емкость и различные усилительные свойства.

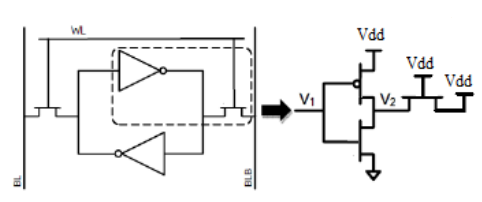

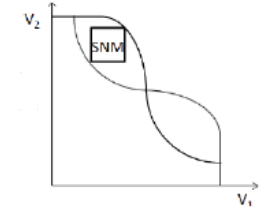

Для характеризации ячеек памяти и оценки их помехоустойчивости водится такой параметр, как статический запас помехоустойчивости (Static Noise Margin — SNM). Что бы определить «SNM» необходимо выполнить наложение графиков передаточных характеристик двух инверторов статической ячейки памяти (Рисунок 3), которые образуют триггер. Сторона квадрата, полученная при наложении двух характеристик, является искомой величиной SNM (Рисунок 4).

Рис. 3. Эквивалентная схема для определения значения SNM

Рис. 4. График передаточных характеристик двух инверторов

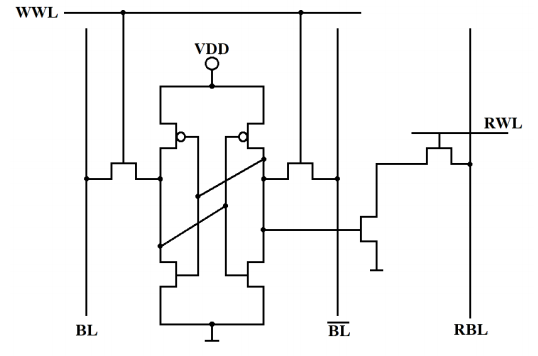

При отсутствии достоверной информации о технологический разбросов параметров во время производства памяти практически невозможно реализовать необходимый запас помехоустойчивости 6-ти транзисторной статической ячейки памяти. Для решения данной проблемы используют 8-ми транзисторную ячейку памяти (Рисунок 5), которая позволяет разделить операции чтения и записи.

Рис. 5. Схема 8-ми транзисторной статической ячейки памяти: RWL — Read Word Line; WL — World Line; BL — Bit Line

Линия WWL управляет затворами двух полевых транзисторов. Линия BL — битовые линии, необходимы для записи данных (в 6-ти транзисторной ячейки памяти данные линии осуществляют как функцию записи, так и функцию чтения). Во время процесса считывания в 8-ми транзисторной ячейке памяти подается сигнал на линию RWL, исходя из того какая информация хранилась в ячейки, мы имеем инверсный сигнал на выходной линии RBL. Запись в данной ячейки памяти реализована таким же образом, как и в 6-ти транзисторной ячейки памяти.

Вывод.

Одна из возможностей достижения быстродействия и стабильности ячеек памяти является разделения портов записи и чтения. Добавление двух транзисторов в 8-ми транзисторной ячейки памяти ведет к значительной прибавки к площади всей памяти, однако это значительно компенсируется улучшением временными параметрами, а также возможностью реализации многопортовой памяти.

Похожие статьи

Общая структура памяти спроизвольным доступом

Динамическая память относительно статической является недорогой в изготовлении и имеет большую плотность компоновки ячеек (Рисунок 4). Стандартная ячейка динамической памяти обычно в своей структуре имеет два элемента.

Основные особенности статических оперативных запоминающих.

Keywords: static random access memory, triggers, memory, rows, columns, matrix, control signals.

Ячейка памяти постоянно находится в состоянии логического нуля или логической единицы.

Метастабильное состояние триггера и способы его устранения

Существует специальный аппаратный блок — двухпортовая память с независимыми тактовыми сигналами (dual-port RAM).

Заодно логика FIFO следит за тем, чтобы не происходило обращения к одной и той же ячейке памяти.

Анализ и выбор тестовых алгоритмов для проведения.

В наши дни острой проблемой является тестирование интегральных микросхем памяти.

– Квадратичные алгоритмы ( ) применяют для контроля функционирования ЗУ всех типов и обнаружения динамических и статических неисправностей.

Сравнение быстродействия и помехоустойчивости ТТЛ.

ТТЛ (транзисторно-транзисторная логика) и КМОП (комплементарные МОП-структуры) представляют собой два наиболее распространённых семейства логических элементов.

3.2. Определение статической помехоустойчивости.

Пути, приемы и средства улучшения памяти | «Молодой

Существует множество способов управления и тренировки памяти. Каждый человек хотел бы улучшить память, но не всякий знает, что для этого нужно. Самое главное правило для улучшения памяти гласит: «Чтобы развить память ее надо развивать».

Составные модули и алгоритмы базовых функций контроллера.

Регистр команды не занимает адресуемой ячейки памяти. Этот регистр содержит команду, вместе с любыми адресами и информацией о данных, необходимых для выполнения команды.

Разработка способа представления длинных чисел в памяти.

Из различных способов представления длинных чисел в памяти компьютера для разработки программного продукта был выбран и доработан

Число 10000 было выбрано за размер одной ячейки во избежание перегрузки элемента списка при выполнении промежуточных расчетов.

Анализ уязвимости переполнения буфера | Статья в журнале.

Куча — специальная область памяти, которую программа способна запрашивать динамически во время выполнения. Кроме того, что сами блоки памяти могут содержать важную для программы информацию, в выделенных из кучи участках содержатся служебные данные.

# факты | Как работает оперативная память?

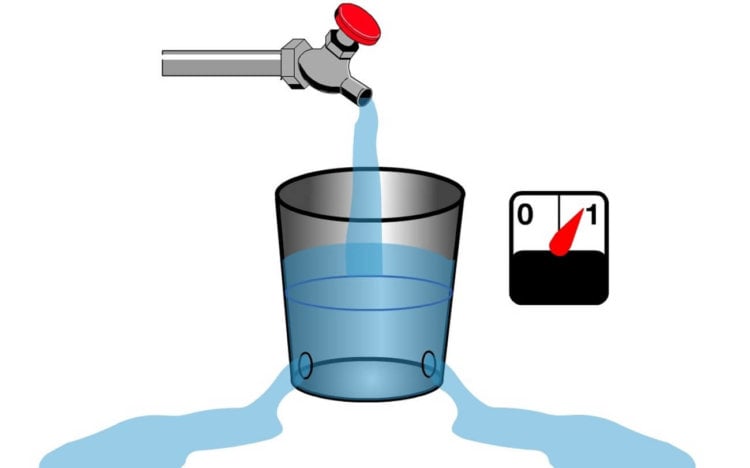

Оперативная память (ОЗУ, RAM), самая известная из всех рассмотренных ранее форм компьютерной памяти. Эту память называют памятью «произвольного доступа» («random access»), поскольку вы можете получить доступ к любой ее ячейке непосредственно. Для этого достаточно знать строку и столбец, на пересечении которых находится нужная ячейка. Известны два основных вида оперативной памяти: динамическая и статическая. Сегодня мы подробно рассмотрим принцип «дырявого ведра», на котором основана динамическая память. Некоторое внимание будет уделено и статической памяти, быстрой, но дорогой.

Ячейка памяти подобна дырявому ведру

Подобно подробно рассмотренному ранее микропроцессору, чип памяти является интегральной микросхемой (ИС, IC), собранной из миллионов транзисторов и конденсаторов. Одним из наиболее распространенных видов памяти произвольного доступа является DRAM (динамическая память произвольного доступа, dynamic random access memory). В ней транзистор и конденсатор спарены и именно они образуют ячейку, содержащую один бит информации. Конденсатор содержит один бит информации, то есть «0» или «1». Транзистор же играет в этой паре роль переключателя (свитча), позволяющего управляющей схеме чипа памяти считывать или менять состояние конденсатора.

Конденсатор можно представить себе в виде небольшого дырявого «ведерка», которое при необходимости заполняется электронами. Если оно заполнено электронами, его состояние равно единице. Если опустошено, то нулю. Проблемой конденсатора является утечка. За считанные миллисекунды (тысячные доли секунды) полный конденсатор становится пустым. А это значит, что или центральный процессор, или контроллер памяти вынужден постоянно подзаряжать каждый из конденсаторов, поддерживая его в наполненном состоянии. Подзарядку следует осуществлять до того, как конденсатор разрядится. С этой целью контроллер памяти осуществляет чтение памяти, а затем вновь записывает в нее данные. Это действие обновления состояния памяти осуществляется автоматически тысячи раз за одну только секунду.

Конденсатор динамической оперативной памяти можно сравнить с протекающим ведром. Если его не заполнять электронами снова и снова, его состояние станет нулевым. Именно эта операция обновления и внесла в название данного вида памяти слово «динамическая». Такая память или обновляется динамически, или «забывает» все, что она «помнила». Есть у этой памяти существенный недостаток: необходимость постоянно обновлять ее требует времени и замедляет работу памяти.

Устройство ячейки динамической оперативной памяти (DRAM)

Итак, представим себе тетрадный лист. Некоторые клеточки закрашены красным фломастером, а некоторые остались белыми. Красные клеточки это ячейки, состояние которых «1», а белые — «0».

Только вместо листа из тетради в оперативной памяти используется кремниевая пластина, в которую «впечатаны» столбцы (разрядные линии, bitlines) и строки (словарные шины, wordlines). Пересечение столбца и строки является адресом ячейки оперативной памяти.

Динамическая оперативная память передает заряд по определенному столбцу. Этот заряд называют стробом адреса столбца (CAS, Column Adress Strobe) или просто сигналом CAS. Этот сигнал может активировать транзистор любого бита столбца. Управляющий сигнал строки именуется стробом адреса строки (RAS, Row Adress Strobe). Для указания адреса ячейки следует задать оба управляющих сигнала. В процессе записи конденсатор готов принять в себя заряд. В процессе чтения усилитель считывания (sense-amplifier) определяет уровень заряда конденсатора. Если он выше 50 %, бит читается, как «1»; в остальных случаях, как «0».

Осуществляется также обновление заряда ячеек. За порядком обновления следит счетчик. Время, которое требуется на все эти операции, измеряется в наносекундах (миллиардных долях секунды). Если чип памяти 70-наносекундный, это значит, полное чтение и перезарядка всех его ячеек займет 70 наносекунд.

Сами по себе ячейки были бы бесполезны, если бы не существовало способа записать в них информацию и считать ее оттуда. Соответственно, помимо самих ячеек, чип памяти содержит целый набор дополнительных микросхем. Эти микросхемы выполняют следующие функции:

У контроллера памяти есть и другие функции. Он выполняет набор обслуживающих задач, среди которых следует отметить идентификацию типа, скорости и объема памяти, а также проверку ее на ошибки.

Статическая оперативная память

Статическая оперативная память быстрее, но и стоит дороже. По этой причине статическая память используется в кэше центрального процессора, а динамическая в качестве системной оперативной памяти компьютера. Более подробно о статической памяти написано в разделе «Кэш-память и регистр процессора» материала, посвященного преодолению ограничений компьютерной памяти.

В современном мире чипы памяти комплектуются в компонент, именуемый модулем. Порой компьютерные специалисты называют его «планкой памяти». Один модуль или «планка» содержит несколько чипов памяти. Не исключено, что вам приходилось слышать такие определения, как «память 8×32» или «память 4×16». Разумеется, цифры могли быть иными. В этой простой формуле первым множителем является количество чипов в модуле, а вторым емкость каждого модуля. Только не в мегабайтах, а в мегабитах. Это значит, что результат действия умножения следует разделить на восемь, чтобы получить объем модуля в привычных нам мегабайтах.

К примеру: 4×32 означает, что модуль содержит четыре 32-мегабитных чипа. Умножив 4 на 32, получаем 128 мегабит. Поскольку нам известно, что в одном байте восемь бит, нам нужно разделить 128 на 8. В итоге узнаем, что «модуль 4×32» является 16-мегабайтным и устарел еще в конце минувшего века, что не мешает ему быть превосходным простым примером для тех вычислений, которые нам потребовались.

Тема оперативной памяти настолько обширна, что мы вернемся к ней еще. Нам предстоит узнать о том, какие бывают типы оперативной памяти и как устроен ее модуль. Продолжение следует…

Национальная библиотека им. Н. Э. Баумана

Bauman National Library

Персональные инструменты

SRAM (Static Random Access Memory)

Содержание

История

Принципы функционирования SRAM

Устройство матрицы статической памяти

Подобно ячейкам динамической памяти триггеры объединяются в единую матрицу, состоящую из строк (row) и столбцов (column), последние из которых так же называются битами (bit).

Этого ограничения лишена многопортовая память. Каждая ячейка многопортовой памяти содержит один-единственный триггер, но имеет несколько комплектов управляющих транзисторов, каждый из которых подключен к «своим» линиям ROW и BIT, благодаря чему различные ячейки матрицы могут обрабатываться независимо. Такой подход намного более прогрессивен, чем деление памяти на банки. Ведь, в последнем случае параллелизм достигается лишь при обращении к ячейкам различных банков, что не всегда выполнимо, а много портовая память допускает одновременную обработку любых ячеек, избавляя программиста от необходимости вникать в особенности ее архитектуры. (Замечание: печально, но кэш-память x86-процессор не истинно многопортовая, а состоит из восьми одно-портовых матриц, подключенных к двух портовой интерфейсной обвязке)

Устройство интерфейсной обвязки

Номера столбцов и строк поступают на декодеры столбца и строки соответственно. После декодирования расшифрованный номер строки поступает на дополнительный декодер, вычисляющий, принадлежащую ей матрицу. Оттуда он попадает непосредственно на выборщик строки, который открывает «защелки» требуемой страницы. В зависимости от выбранного режима работы чувствительный усилитель, подсоединенный к битовым линейкам матрицы, либо считывает состояние триггеров соответствующей raw-линейки, либо «перещелкает» их согласно записываемой информации.

Временные диаграммы чтения/записи

Цикл записи

Цикл записи происходит в обратном порядке. Сначала мы выставляем на шину адрес записываемой ячейки и одновременно с этим сбрасываем сигнал WE в низкое состояние. Затем, дождавшись, когда наш адрес декодируется, усилиться и поступит на соответствующие битовые линии, сбрасываем CS в низкий уровень, приказывая микросхеме подать сигнал высокого уровня на требуемую линию row. Защелка, удерживающая триггер, откроется и в зависимости от состоянии bit-линии, триггер переключится в то или иное состояние.

Сравнение DRAM и SRAM в компьютерной среде

По сравнению с DRAM быстродействие SRAM намного выше, но плотность ее гораздо ниже, а цена довольно высока. Более низкая плотность означает, что микросхемы SRAM имеют большие габариты, хотя их информационная емкость намного меньше. Большое число транзисторов и кластеризованное их размещение не только увеличивает габариты микросхем SRAM, но и значительно повышает стоимость технологического процесса по сравнению с аналогичными параметрами для микросхем DRAM. Например, емкость модуля DRAM может равняться 64 Мбайт или больше, в то время как емкость модуля SRAM приблизительно того же размера составляет только 2 Мбайт, причем их стоимость будет одинаковой. Таким образом, габариты SRAM в среднем в 30 раз превышают размеры DRAM, то же самое можно сказать и о стоимости. Все это не позволяет использовать память типа SRAM в качестве оперативной памяти в персональных компьютерах.

Несмотря на это разработчики все-таки применяют память типа SRAM для повышения эффективности ПК. Но во избежание значительного повышения стоимости устанавливается только небольшой объем высокоскоростной памяти SRAM, которая используется в качестве кэш-памяти. Кэш-память работает на тактовых частотах, близких или даже равных тактовым частотам процессора, причем обычно именно эта память непосредственно используется процессором при чтении и записи. Во время операций чтения данные в высокоскоростную кэш-память предварительно записываются из оперативной памяти с низким быстродействием, т.е. из DRAM. Еще недавно время доступа DRAM было не менее 60 нс (что соответствует тактовой частоте 16 МГц). Для преобразования времени доступа из наносекунд в мегагерцы используется следующая формула:

Обратное вычисление осуществляется с помощью такой формулы:

Сегодня память может работать на частоте 1 ГГц и выше, однако до конца 1990-х годов память DRAM была ограничена быстродействием 16 нс (16 МГц). Когда процессор ПК работал на тактовой частоте 16 МГц и ниже, DRAM могла быть синхронизирована с системной платой и процессором, поэтому кэш был не нужен. Как только тактовая частота процессора поднялась выше 16 МГц, синхронизировать DRAM с процессором стало невозможно, и именно тогда разработчики начали использовать SRAM в персональных компьютерах. Это произошло в 1986 и 1987 годах, когда появились компьютеры с процессором 386, работающим на частотах 16 и 20 МГц. Именно в этих ПК впервые нашла применение так называемая кэшпамять, т.е. высокоскоростной буфер, построенный на микросхемах SRAM, который непосредственно обменивается данными с процессором. Поскольку быстродействие кэша может быть сравнимо с процессорным, контроллер кэша может предугадывать потребности процессора в данных и предварительно загружать необходимые данные в высокоскоростную кэшпамять. Тогда при выдаче процессором адреса памяти данные могут быть переданы из высокоскоростного кэша, а не из оперативной памяти, быстродействие которой намного ниже.

Типы статической памяти

Существует как минимум три типа статической памяти: асинхронная (только что рассмотренная выше), синхронная и конвейерная. Все они практически ничем не отличаются от соответствующих им типов динамической памяти, поэтому, во избежание никому не нужного повторения ниже приведено лишь краткое их описание.

Асинхронная статическая память

Синхронная статическая память

Синхронная статическая память выполняет все операции одновременно с тактовыми сигналами, в результате чего время доступа к ячейке укладывается в один-единственный такт. Именно на синхронной статической памяти реализуется кэш первого уровня современных процессоров.

Конвейерная статическая память

Конвейерная статическая память представляет собой синхронную статическую память, оснащенную специальными «защелками», удерживающими линии данных, что позволяет читать (записывать) содержимое одной ячейки параллельно с передачей адреса другой. Так же, конвейерная память может обрабатывать несколько смежных ячеек за один рабочий цикл. Достаточно передать лишь адрес первой ячейки пакета, а адреса остальных микросхема вычислит самостоятельно За счет большей аппаратной сложности конвейерной памяти, время доступа к первой ячейке пакета увеличивается на один такт, однако, это практически не снижает производительности, т.к. все последующие ячейки пакета обрабатываются без задержек.

Статическая оперативная память

Статическая память (SRAM) – это энергозависимая полупроводниковая память с произвольным доступом, в которой каждый разряд хранится в триггере, позволяющем поддерживать состояние разряда без постоянной перезаписи. Для организации чтения и записи из ячейки памяти дополнительно используется три или более транзисторов.

Содержание.

1. Устройство триггера.

Для того чтобы понять принцип работы статической памяти, обратимся к истокам схемотехники. И начнем с описания принципа работы триггера, изображенного на рисунке 1.

Триггер – это элемент памяти с двумя стабильными состояниями – «0» и «1». В установленном состоянии триггер сохраняется, пока на него подается питание.

Обычно триггер имеет два входа:

и два выхода: Q и инвертированное Q (

Входы R и S используются для установки состояния триггера. Если на вход S подать напряжение, соответствующее логической единице (далее просто логическую единицу), а на вход R – напряжение, соответствующее логическому нулю (далее просто логический ноль), то триггер перейдет в состояние единицы и сохранит это состояние даже, если на вход S перестать подавать сигнал.

Если на вход S подать логический ноль, а на вход R – логическую единицу, то триггер перейдет в состоянии сохранения нуля.

При подаче на оба входа логического нуля, состояние триггера не измениться.

При подаче на оба входа логической единицы, в общем случае состояние триггера будет неопределенно, то есть неизвестно, в какое состояние он перейдет.

На выходах Q и

В таблице 1 приводится перечень всех возможных состояний триггера.

| S | R | Qi | Qi+1 |  i i |  i+1 i+1 |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | ? | 1 | ? |

| 1 | 1 | 1 | ? | 0 | ? |

Таблица 1. Состояния триггера, в зависимости от сигналов на входе.

Рассмотрев логику работы триггера, давайте разберемся, как же он устроен. Структурная схема триггера приведена на рисунке 2.

Как видно из рисунка, состоит он из двух инвертеров (логических элементов «НЕ»), причем выход одного инвертера замкнут на вход другого.

Давайте рассмотрим, как же работают эти инвертеры при подаче различных сигналов на вход.

Первый случай, на вход S подана логическая единица, а на вход R – логический ноль, то есть установка триггера в единичное состояние. И так, если на вход S подать логическую единицу, то, пройдя через инвертер D.D2, она примет значение логического нуля. Таким образом, на выходе

Если сигналы с входов снять (на вход S и R подать логический ноль), то состояние триггера не изменится. Логическая единица с выхода инвертера D.D1 пойдет на вход инвертера D.D2, а логический ноль с выхода D.D2 пойдет на вход инвертера D.D1, в результате чего на выходе инвертера D.D1 будет логическая единица. То есть мы замкнули цикл, который будет продолжаться до тех пор, пока будет на триггер подводиться питание. Зачем нужно питание, рассмотрим чуть позже, когда будем разбирать принцип устройства инвертера.

Рассмотрим второй случай, когда на вход S подан логический ноль, а на вход R –логическая единица, то есть сброс триггера. И так, если на вход S подать логический ноль, то, пройдя через инвертер D.D2, он примет значение логической единицы. Таким образом, на выходе

Так же, как и в первом случае, при снятии сигналов с входов R и S состояние триггера не изменится.

Давайте теперь более подробно рассмотрим принцип работы инвертера. Существуют различные способы организации инвертера, мы рассмотрим только один из них, самый простой. Этого будет вполне достаточно, чтобы понять принцип его организации. И так на рисунке 4 изображена структурная схема инвертера.

На рисунке представлена простейшая схема реализации инвертера, состоящая из одного транзистора. Давайте рассмотрим, как он работает.

На элемент всегда подается питание Uп. В результате, создаваемый ток может пойти либо по линии AB, в этом случае на выходе инвертера ток будет отсутствовать (будет логический ноль), либо – по линии AC, в этом случае на выходе инвертера ток будет присутствовать (будет логическая единица).

По линии AB ток пойдет, если транзистор VT1 будет открыт, а для этого необходимо подать напряжение на вход инвертера.

По линии AC ток пойдет, если транзистор VT1 будет закрыт, а это произойдет при отсутствии напряжении на входе инвертера.

Таким образом, если на вход инвертера подается логическая единица, то на выходе будет логический ноль. И, соответственно, при подаче на вход инвертера логического нуля, на выходе будет поучена логическая единица.

2. Устройство ячейки статической памяти.

Теперь, зная, как работает триггер и инвертер, рассмотрим устройство ячейки статической памяти и принцип ее работы. Естественно, рассматривать мы будем простейшую ячейку памяти. На практике используют множество дополнительных ухищрений для повышения скорости работы статической памяти. Но, зная принцип работы элементарной ячейки статической памяти, вы без особого труда в дальнейшем разберетесь и в принципе работы других реализаций ячеек статической памяти.

На рисунке 4 приведена упрощенная схема одного из способов организации ячейки статической памяти.

Как видите, она состоит из одного триггера и трех транзисторов, выполняющих роль ключей, открывающих и закрывающих доступ к ячейке памяти. Транзисторы VT1 и VT2 используются для разрешения и запрета записи в ячейку, а транзистор VT3 – для разрешения и запрета чтения.

Для записи данных необходимо подать напряжение в линию строки, после чего транзисторы VT1, VT2 и VT3 откроются. Затем для записи единицы необходимо подать напряжение, соответствующее логической единице, на линию D и напряжение, соответствующее логическому нулю, на линию

В установленном состоянии триггер будет оставаться даже после снятия напряжения с линии строки и с линий D и

Для считывания данных необходимо на выходы D и

Считывание данных с ячейки статической памяти, в отличие от чтения с ячейки динамической памяти, не приводит к потере сохраненного бита данных, поэтому, перезапись данных в ячейку статической памяти не требуется.

3. Устройство микросхемы статической памяти.

Давайте перейдем к следующему этапу изучения работы статической памяти и рассмотрим ее общую логику работы. Для этого обратимся к упрощенной структурной схеме статической памяти, изображенной на рисунке 5.

Начнем с записи данных в статическую память и рассмотрим случай записи единицы в ячейку М11.

В контроллер шины памяти от контроллера памяти, встроенного в северный мост материнской платы или в процессор, приходит адрес ячейки памяти и данные для записи. Адрес ячейки преобразуется на две составляющие – номер строки и номер столбца. Номер строки передается в «Дешифратор адреса строки», откуда на нужную строку подается напряжение.

Так как мы рассматриваем запись в ячейку М11, то напряжение с дешифратора адреса строки подается на первую строку. В результате, транзисторы VT1, VT2 и VT3 открываются. Аналогичные транзисторы других ячеек памяти, располагающихся в этой строке, также открываются.

Через транзистор VT3 первой ячейки и аналогичные транзисторы других ячеек памяти первой строки пойдет ток, соответствующий состоянию триггеров этих ячеек, в «Буфер данных». Однако «Буфер данных» получаемую информацию будет игнорировать, так как у него нет сигнала от «Блока управления» на сохранение считываемых данных.

Блоки записи используются для запрета выдачи тока в линии D и

В нашем случае, запись проводится в ячейку М11, и записывается единица. Соответственно, с «Блока работы с данными» будет выдана логическая единица в «Блок записи 1», и с «Блока дешифровки адреса столбца» будет выдана логическая единица в «Блок записи 1».

Рассмотрим работу «Блока записи 1» при таких входных сигналах. И так, на входе элемента D.D3 будет логическая единица, а на выходе – логический ноль, так как элемент D.D3 – инвертер (логический элемент «НЕ»). Соответственно, на входах элемента D.D4 (логический элемент «И») будут: логический ноль и логическая единица. В результате, на выходе этого элемента будет логический ноль.

На входах элемента D.D5 (логический элемент «И») будут две логические единицы, в результате, на выходе этого элемента будет логический ноль.

Следовательно, на выходе D1 «Блока записи 1» будет напряжение, соответствующее логическому нулю, а на выходе

После изменения состояния триггера первой ячейки напряжение с первой строки снимается, и транзисторы VT1, VT2 и VT3 закрываются, запрещая запись и чтение из ячейки.

При записи нуля в ячейку памяти все происходит по той же схеме, только с «Блока работы с данными» в «Блок записи 1» будет подано напряжение, соответствующее логическому нулю. Это значит, что на выходе D1 «Блока записи 1» будет напряжение, соответствующее логической единице, а на выходе

В установленном состоянии триггер первой ячейки останется, пока на него будет подаваться питание Uп.

Чтение записи происходит еще проще. От контроллера памяти приходит адрес ячеек памяти, с которых требуется считать данные, и команда на чтение.

В результате, адрес преобразуется в номер строки, и на соответствующую строку будет подано напряжение, которое откроет транзисторы разрешения/запрета чтения/записи.

Рассмотрим случай, когда данные считываются из первой ячейки. В этом случае напряжение с «Дешифратора адреса строки» будет подано в первую строку, что приведет к открытию транзисторов VT1, VT2 и VT3 ячейки М11 и всех остальных ячеек первой строки. Ток с триггера первой ячейки, через транзистор VT1, беспрепятственно пройдет в «Буфер данных». То же самое произойдет с остальными ячейками первой строки. Считанные с ячеек памяти первой строки данные сохранятся в «Буфере данных».

После того, как информация в «Буфере данных» будет сохранена, «Дешифратор адреса столбцов» выдаст номера столбцов, данные с которых необходимо считать, в «Буфер данных». Соответствующие данные будут переданы из микросхемы памяти в контроллер памяти, располагающийся в материнской плате или непосредственно в процессоре.

Для того чтобы при чтении данных не происходила запись в эти же ячейки, ведь транзисторы, разрешающие запись, открыты, блоки записи выдают в линии D и

Как видите, работа статической памяти очень похожа на работу динамической памяти, однако процесс записи и чтения гораздо быстрее, так как не тратится время на заряд и разряд конденсаторов и не требуется регенерация ячеек. Однако необходимо обратить внимание, что рассмотренная нами схема сильно упрощена, и на практике используют гораздо более сложные механизмы записи и чтения из памяти, повышающие надежность и скорость работы статической памяти. Однако описанный выше принцип работы позволяет понять основы функционирования статической памяти, ее недостатки и преимущества. Давайте попробуем сформулировать их (основные недостатки и преимущества).

4. Достоинства и недостатки статической памяти.

В связи с перечисленными выше достоинствами и недостатками, область применения статической памяти ограничивается, в основном, использованием ее в качестве КЭШ-памяти, что позволяет при небольшом увеличении стоимости уменьшить влияние недостатков динамической памяти на производительность ЭВМ. Однако, это все лишь компромисс, позволяющий несколько сгладить разрыв в производительности процессора и памяти, и все вытекающие отсюда последствия.

Требуется кардинальное решение проблемы существующей с момента зарождения вычислительной техники. Существует множество экспериментальных разработок, позволяющих получить быструю и дешевую оперативную память, но многие из них пока существуют только в виде лабораторных образцов, многие имеют недостаточную надежность и так далее. Наиболее перспективный путь развития оперативной памяти – это использование магниторезистивной памяти, получающей все большее распространение.